In a paper titled "A 3.0 Gsymbol/s/lane MIPI C-PHY Receiver with Adaptive Level-Dependent Equalizer for Mobile CMOS Image Sensor" Choi et al write:

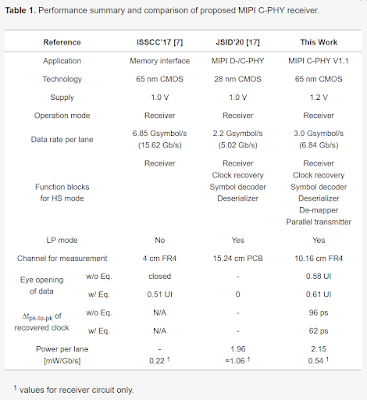

Abstract: A 3.0 Gsymbol/s/lane receiver is proposed herein to acquire near-grounded high-speed signals for the mobile industry processor interface (MIPI) C-PHY version 1.1 specification used for CMOS image sensor interfaces. Adaptive level-dependent equalization is also proposed to improve the signal integrity of the high-speed receivers receiving three-level signals. The proposed adaptive level-dependent equalizer (ALDE) is optimized by adjusting the duty cycle ratio of the clock recovered from the received data to 50%. A pre-determined data pattern transmitted from a MIPI C-PHY transmitter is established to perform the adaptive level-dependent equalization. The proposed MIPI C-PHY receiver with three data lanes is implemented using a 65 nm CMOS process with a 1.2 V supply voltage. The power consumption and area of each lane are 4.9 mW/Gsymbol/s/lane and 0.097 mm2, respectively. The proposed ALDE improves the peak-to-peak time jitter of 12 ps and 34 ps, respectively, for the received data and the recovered clock at a symbol rate of 3 Gsymbol/s/lane. Additionally, the duty cycle ratio of the recovered clock is improved from 42.8% to 48.3%.

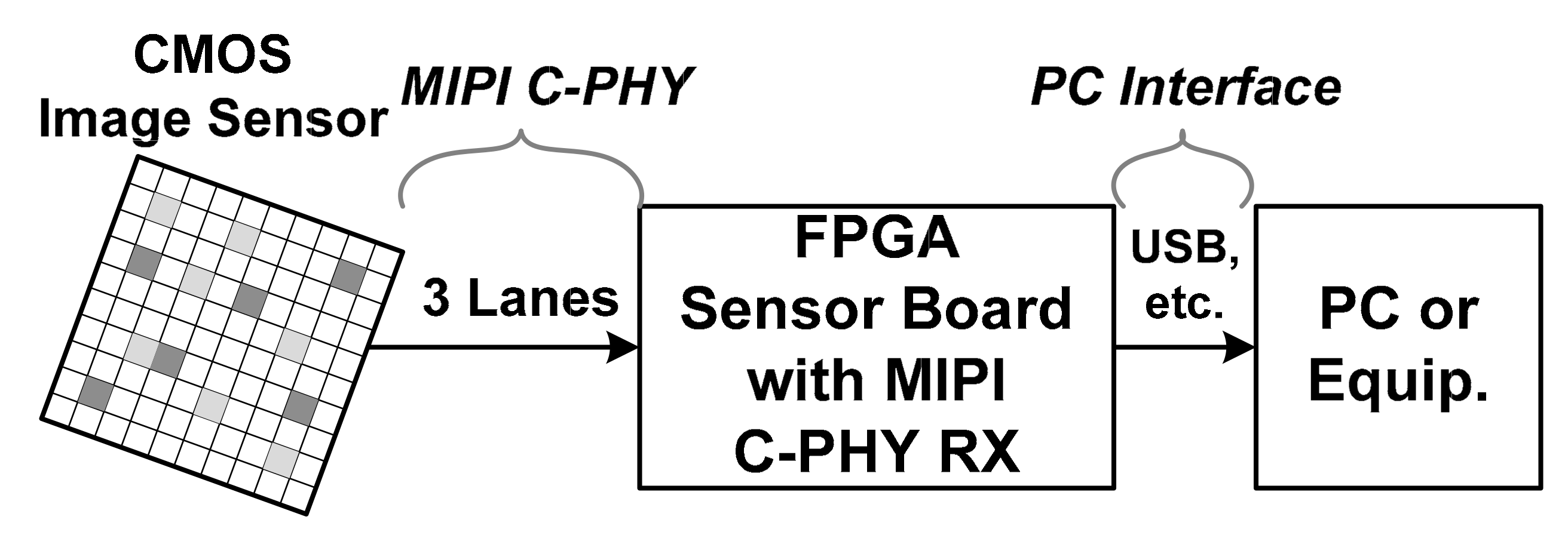

High-speed interface of FPGA-based frame grabber for CMOS image sensor.

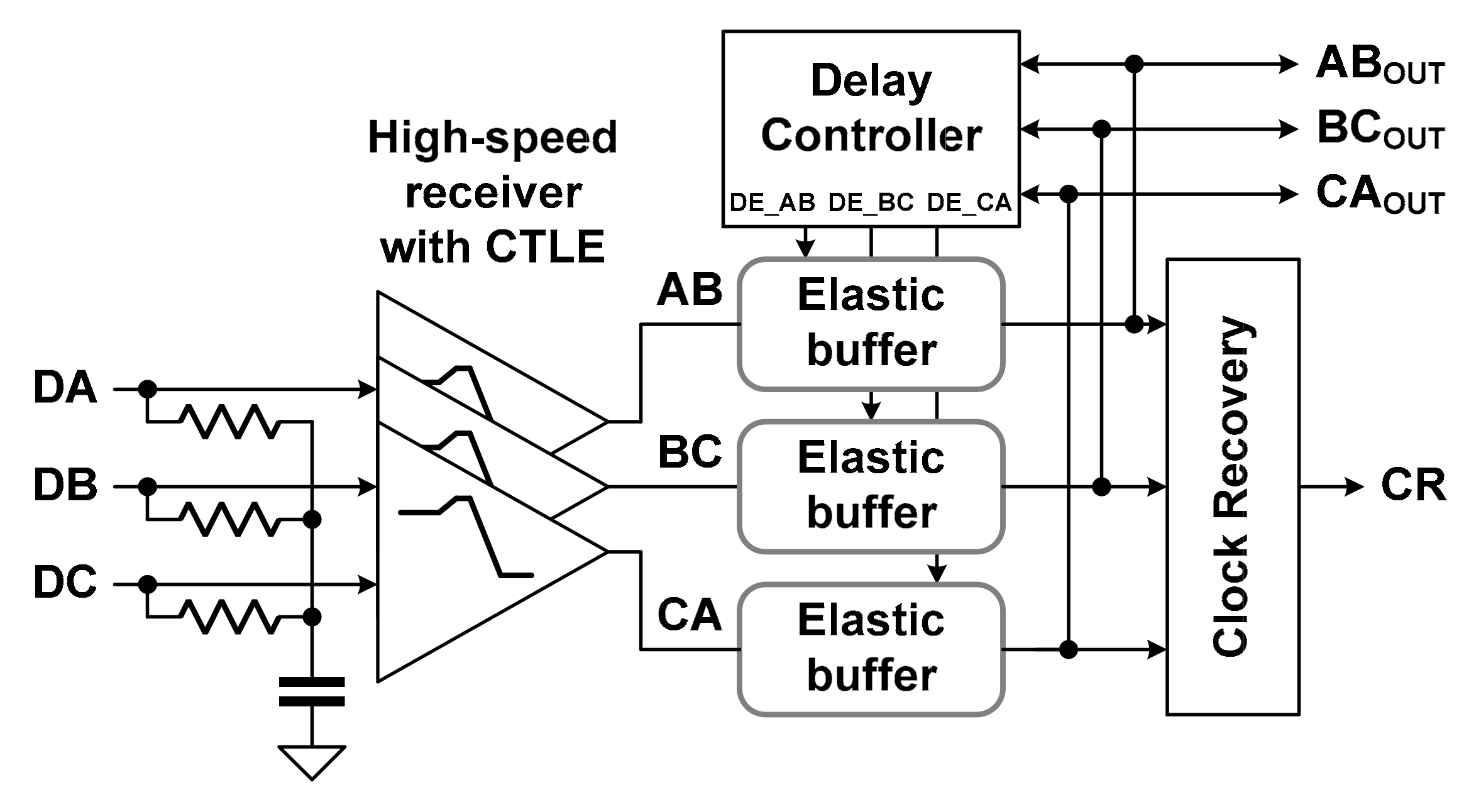

Conventional high-speed receiver using level-dependent elastic buffer for MIPI C-PHY.

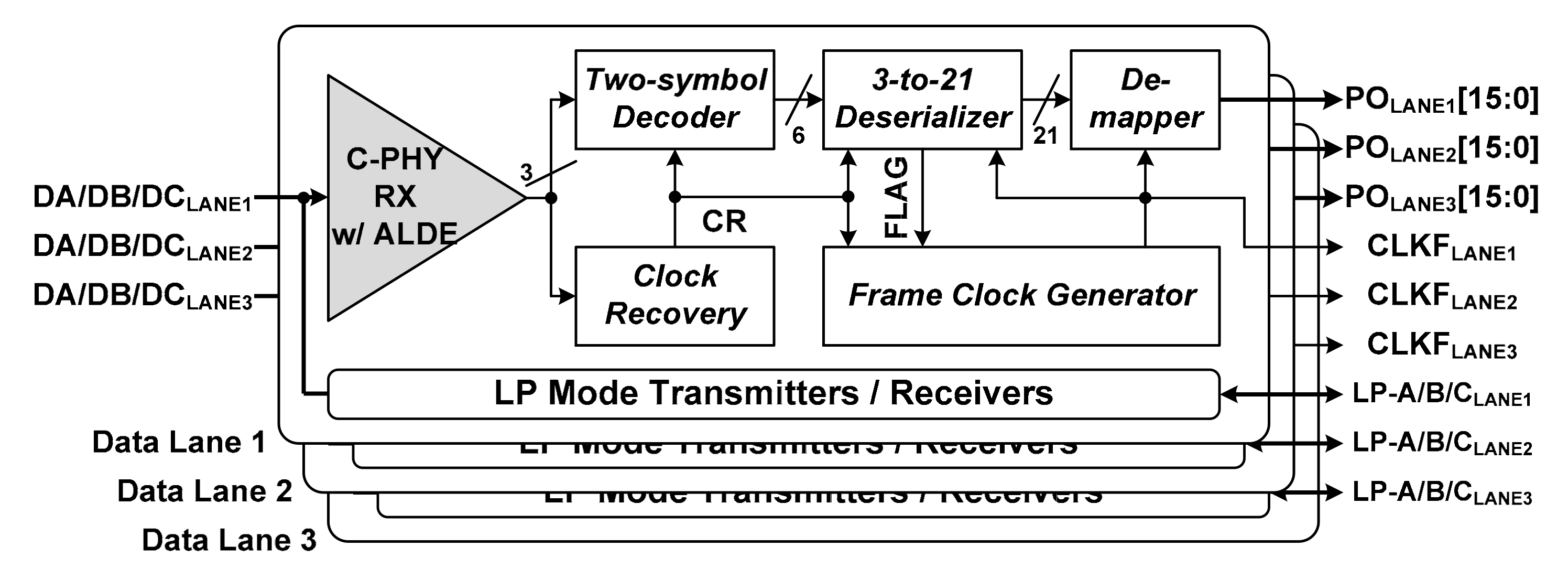

Block diagram of proposed MIPI C-PHY receiver chip.

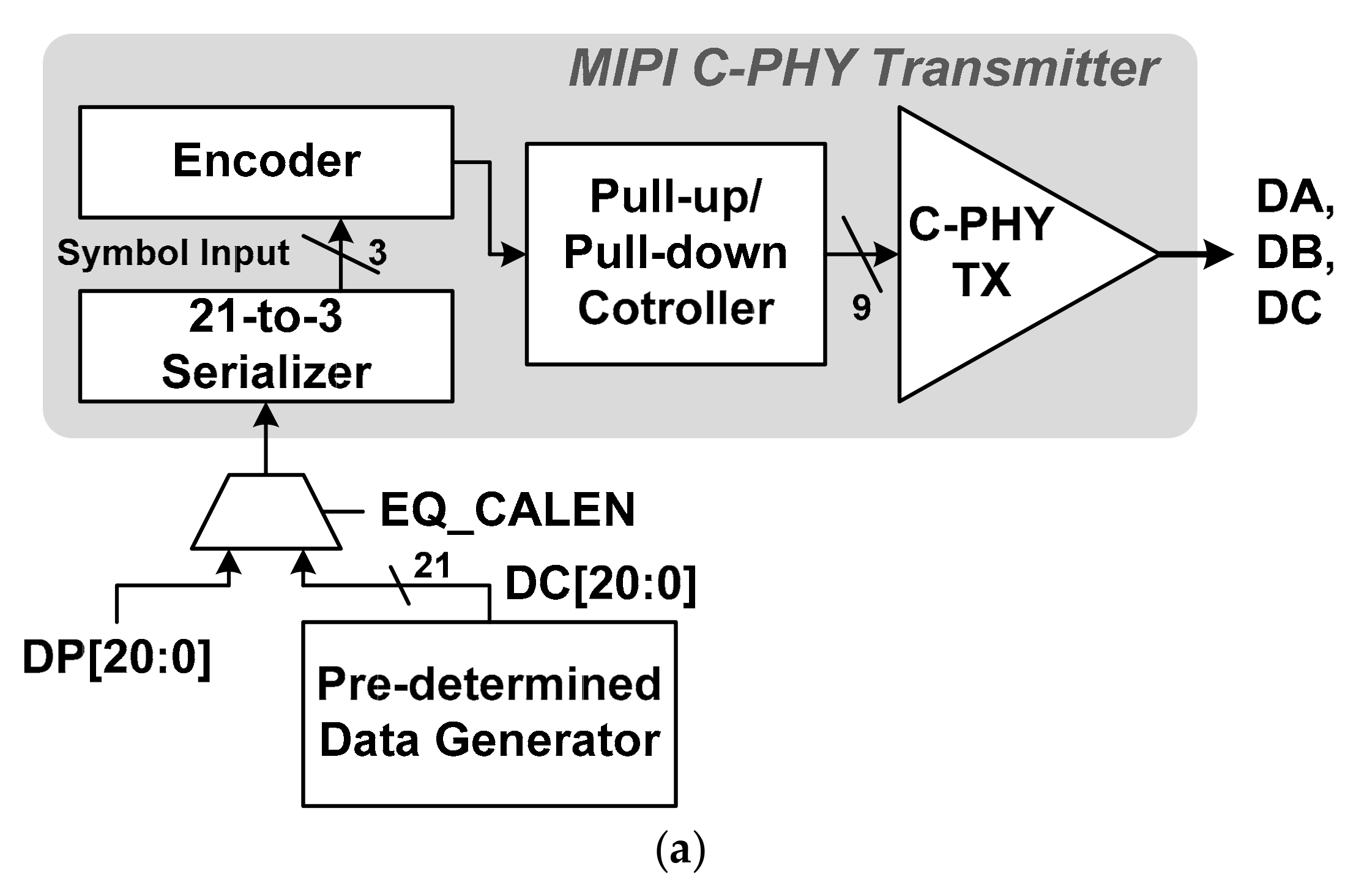

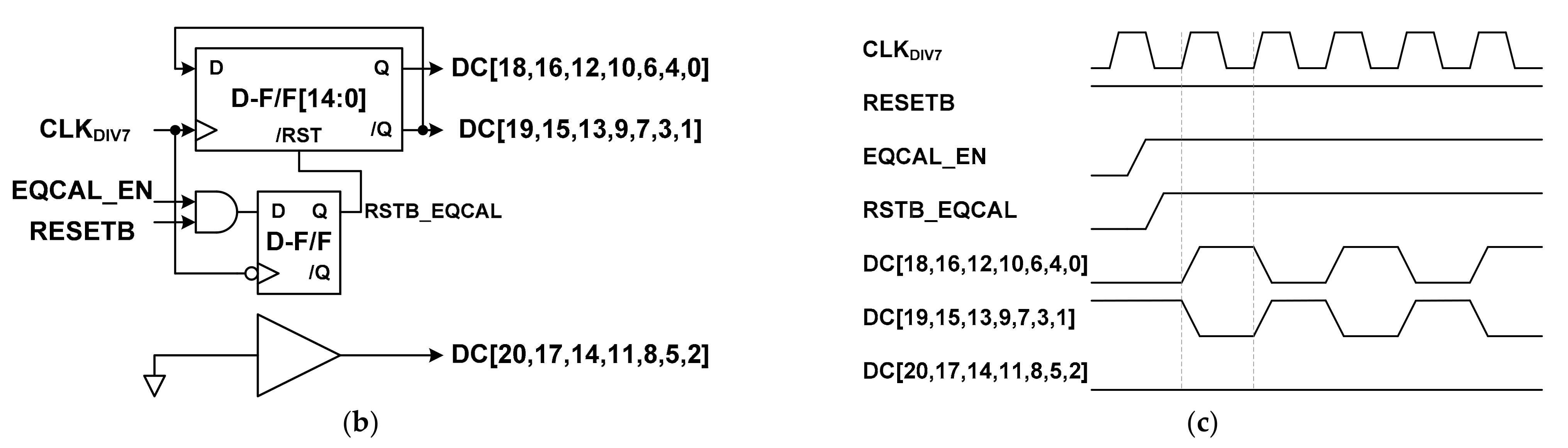

Pre-determined data generator: (a) Connection between MIPI C-PHY transmitter and pre-determined data generator; (b) Block diagram for pre-determined data generator; (c) Time diagram of pre-determined data generator.

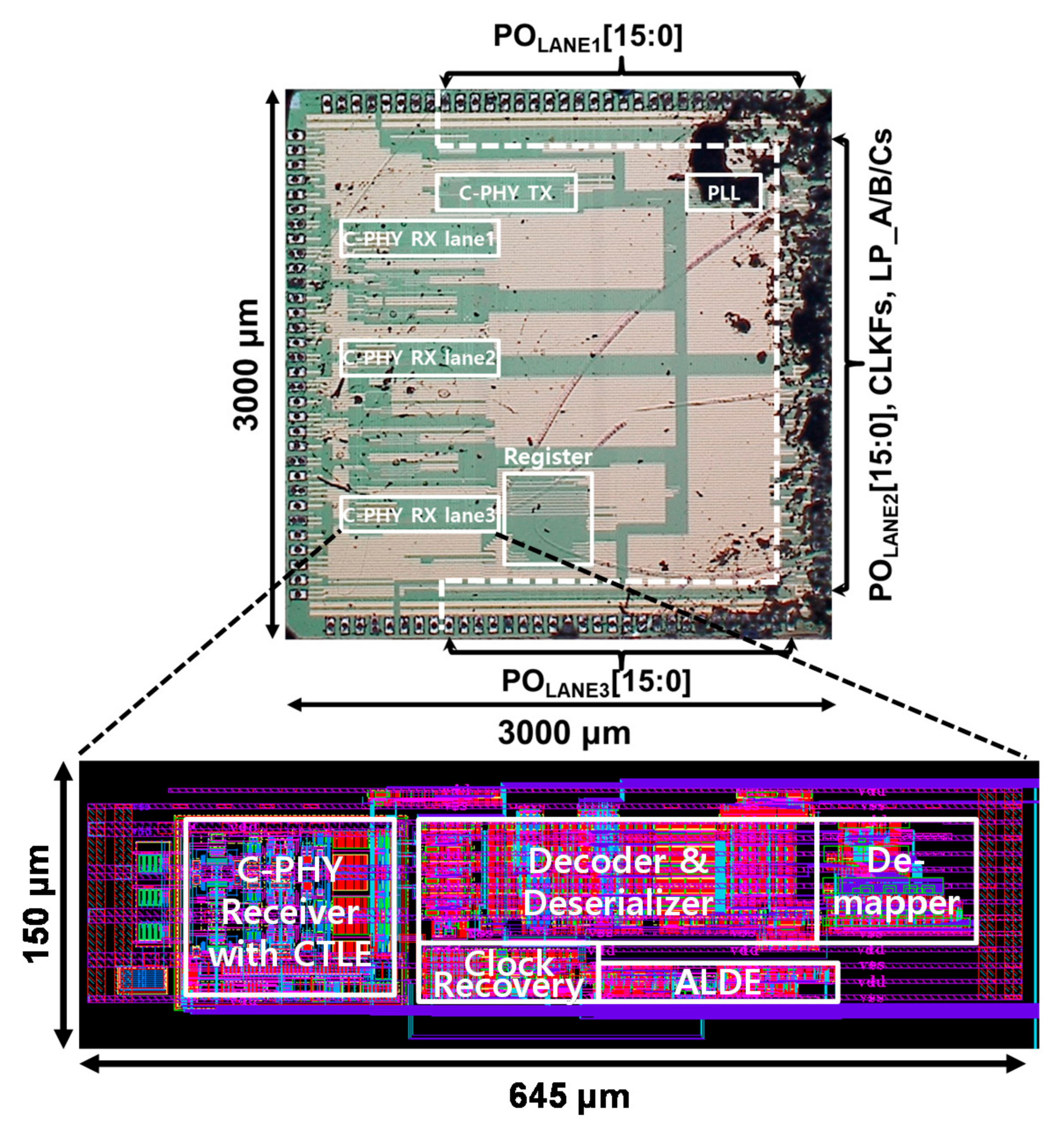

Microphotograph of implemented MIPI C-PHY receiver chip.

I feel like I'm missing something here. Why would a MIPI receiver be aimed a mobile image sensors? In my world sensors use transmitters. Rx goes on the SOC, but at 65nm this is not a match for any modern SOC.

ReplyDeleteIts a research work. You think they have money for a 3nm silicon for a mipi research paper?

DeleteI think this would be helpful for evaluation/validation systems. From the standpoint of a mobile image sensor manufacturer they don't need or don't want to use a state of the art SoC to validate or test their dies. So a standalone C-PHY Receiver IC is quite helpful in the sense that it adds C-PHY support to older gen SoCs or even state of the art FPGAs that don't support C-PHY natively

DeleteMany of us would appreciate a bridge and gearing chip which turns few CPHY trios into few more DPHY lanes, that are then handled by an FPGA. I wonder why this segment needs to invent always some obscure proprietary interface, which can not be implemented easily by a 3rd party.

Delete