Arxiv.org paper "An Ultra Fast Low Power Convolutional Neural Network Image Sensor with Pixel-level Computing" by Ruibing Song, Kejie Huang, Zongsheng Wang, Haibin Shen from Zhejiang University, China, is also published in IEEE Transactions on Circuits and Systems in December 2020.

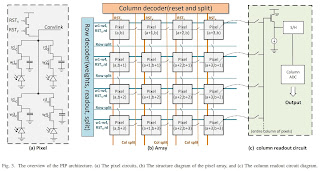

"The separation of the data capture and analysis in modern vision systems has led to a massive amount of data transfer between the end devices and cloud computers, resulting in long latency, slow response, and high power consumption. Efficient hardware architectures are under focused development to enable Artificial Intelligence (AI) at the resource-limited end sensing devices. This paper proposes a Processing-In-Pixel (PIP) CMOS sensor architecture, which allows convolution operation before the column readout circuit to significantly improve the image reading speed with much lower power consumption. The simulation results show that the proposed architecture enables convolution operation (kernel size=3*3, stride=2, input channel=3, output channel=64) in a 1080P image sensor array with only 22.62 mW power consumption. In other words, the computational efficiency is 4.75 TOPS/w, which is about 3.6 times as higher as the state-of-the-art."

No comments:

Post a Comment

All comments are moderated to avoid spam and personal attacks.