Link: http://jiia.org/en/slvs-ec-if-standard-version-3-0-has-been-released/

Embedded Vision I/F WG has released "SLVS-EC IF Standard Version 3.0”.

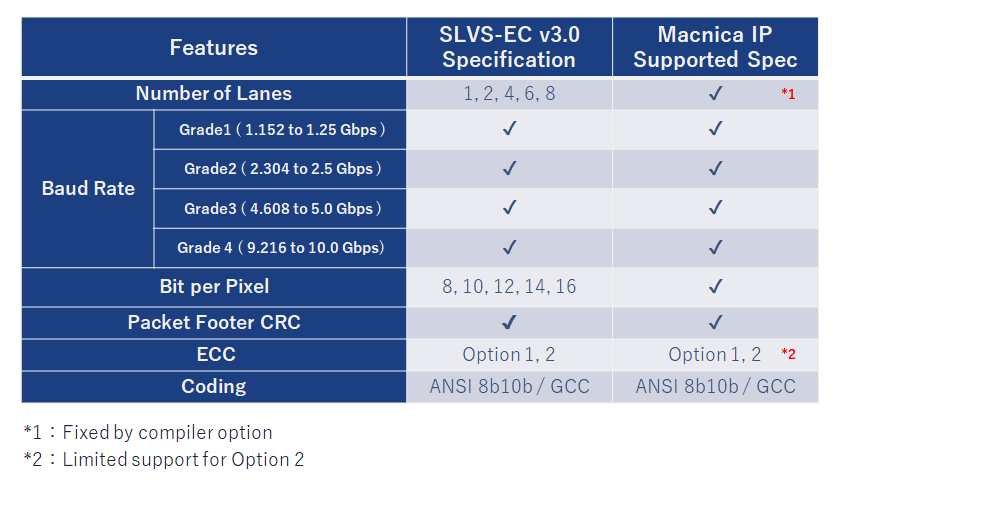

Version 3.0 supports up to 10Gbps/lane, which is 2x faster than Version 2.0, and improved data transmission efficiency.

Link: https://www.m-pression.com/solutions/hardware/slvs-ec-rx-30-ip

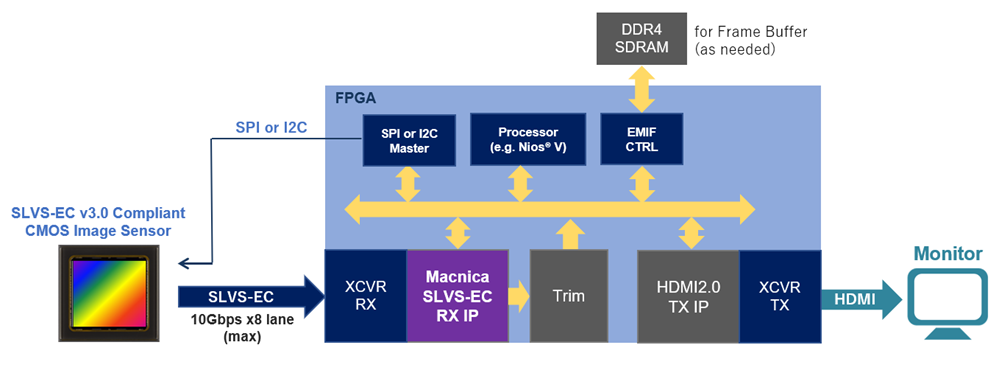

SLVS-EC v3.0 Rx IP is an interface IP core that runs on Altera® FPGAs. Using this IP, you can quickly and easily implement products that support the latest SLVS-EC standard v3.0. You will also receive an "Evaluation kit" for early adoption.- Altera® FPGAs can receive signals directly from the SLVS-EC Interface.

- Compatible with the latest SLVS-EC Specification Version 3.0.

- Supports powerful De-Skew function. Enables board design without considering Skew that occurs between lanes.

- "Evaluation kit”(see below) is available for speedy evaluation at the actual device level.

About SLVS-EC:

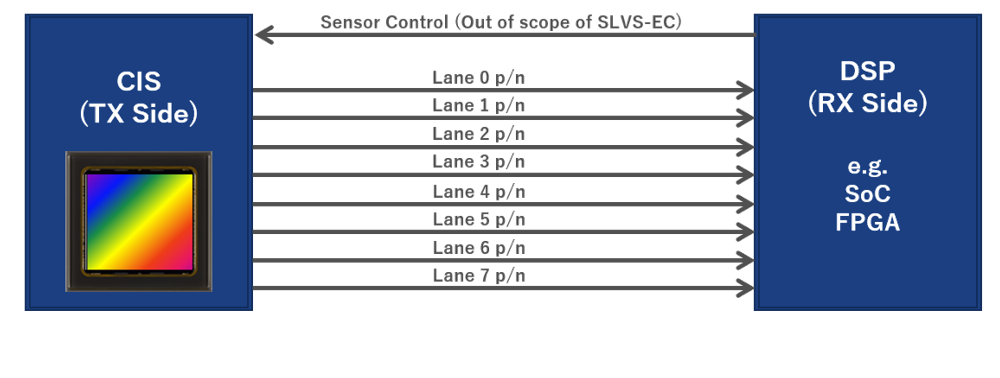

SLVS-EC (Scalable Low Voltage Signaling with Embedded Clock) is an interface standard for high-speed & high-resolution image sensors developed by Sony Semiconductor Solutions Corporation. The SLVS-EC standard is standardized by JIIA (Japan Industrial Imaging Association).

where and under which conditions can be bought the license for this "SLVS-EC IF Standard v3"?

ReplyDeleteHere, but with an obnoxious restriction - http://jiia.org/en/standard_dl/document_db_g3/.

Deletethe first image sensors using the standard are also on the horizon. Few days back Sony announced faster variants of Pregius S 12 and 24MP sensors - IMX925/926/935/936, that are using SLVS-EC V3: https://www.sony-semicon.com/en/products/is/industry/gs/imx925-926.html

ReplyDelete